Marvell's Vision – Custom Silicon, CXL, DPUs, Ethernet, Optical, Telecom, Storage, Automotive, SerDes, 2025 Revenue & EPS

Transforming into the leader in infrastructure silicon & EPS estimates

Marvell recently hosted us at their headquarters in Santa Clara. They described their vision and many product details going forward. The core of it is that Marvell is striving to be the leader in infrastructure silicon. In most cases, Marvell isn’t making the sexy AI accelerators, the beefy datacenter CPU, or the highest I/O switch. Instead, Marvell strives to create the IP and partnerships at the heart of the movement, storage, processing, and security of data.

They likely will be part of all these chips, but not as the sole firm involved. Being the leader in infrastructure requires deep and custom collaboration with the end markets in a way many other semiconductor companies are not technically and culturally set up to do.

The culture of Marvell will be an exciting case study one day. They have doubled their employee count since 2018. The current culture isn’t like the acquired firms or the old Marvell. From talking to many at the firm over the last year, it seems like the culture is a blend of the many people from acquisitions over the previous few years. While everyone got to Marvell with a different path and heritage, the various IP teams still collaborate cohesively.

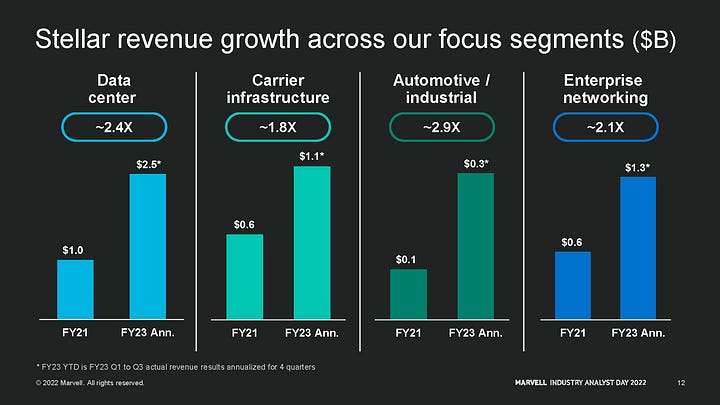

Marvell shared their vision and roadmap with us, and in turn, we will critically analyze it and share where we believe they will succeed and where we are skeptical of their success. Marvell started the day by sharing what they believe are their 4 major verticals, datacenter, telecommunications infrastructure, automotive, and enterprise networking.

This report will discuss those broadly, as well as more specifically about opportunities and competitive positioning for cloud switches, enterprise switches, automotive switches, many major wins with custom hyperscale silicon, HDD controllers, SSD controllers, DSPs, TIAs, pluggable optical transceivers, co-packaged optics, active electrical cables (AECs), infrastructure DPUs, networking DPUs, 5G Baseband and Radio Unit DPUs, 5G Distributed Unit DPUs, security, AI training, AI inference, CXL (9 different product categories being developed), and video ASICs.

This report will also share our FY 2023, 2024, and 2025 revenue and EPS estimates. These estimates were constructed using our bottom-up analysis derived from product line/category revenue estimates.

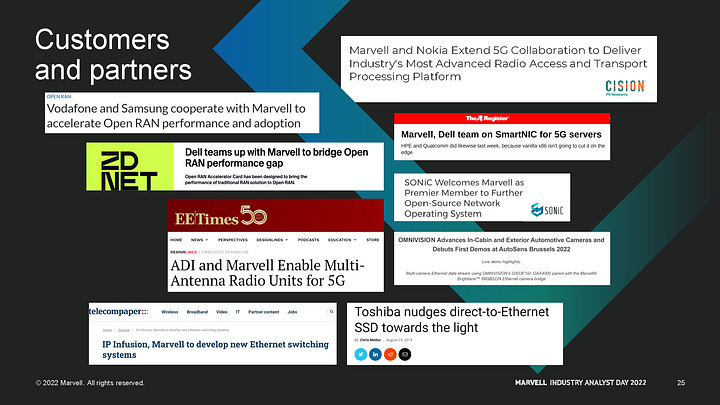

Marvell highlighted the transformation of the business under this framework. In 2019, Marvell had very little penetration in the cloud, only 1 carrier infrastructure OEM partner, a new entrant into automotive, and a distant 2nd in enterprise networking behind Broadcom. This is very different from the Marvell of today.

The Marvell of 2022 is now a leader in many aspects of storage like it always has been by maintaining a #1 position in SSD and HDD controllers and a distant 2nd place to Broadcom. Networking is where Marvell has reshaped their company. The acquisition of Innovium has helped Marvell enter the crowded hyperscale datacenter switch market where Broadcom takes the commanding leadership role and Nvidia, Cisco, and Intel all slug it out. Marvell’s legacy business and the Aquantia-acquired business have a higher share in the enterprise switch market. That Aquantia business is also helping Marvell enter automotive ethernet.

The fantastic Inphi acquisition is helping Marvell lead the PAM4 DSP/TIA and coherent DSP/TIA markets and pick up a tier 2 photonics business. The addition of Cavium has enabled Marvell to become a leader in DPUs and Cloud HSMs. The combination of the Cavium business with the Avera ASIC and custom design business has also enabled Marvell to move into first place for infrastructure 5G baseband processors. The combination of IP from all these acquisitions, as well as the Marvell legacy, is also what may propel them to lead the cloud hyperscale business.

The IP war chest, alongside a collaborative and aggressive culture, makes Marvell one of the foremost semiconductor companies.

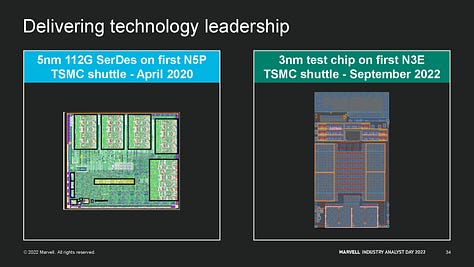

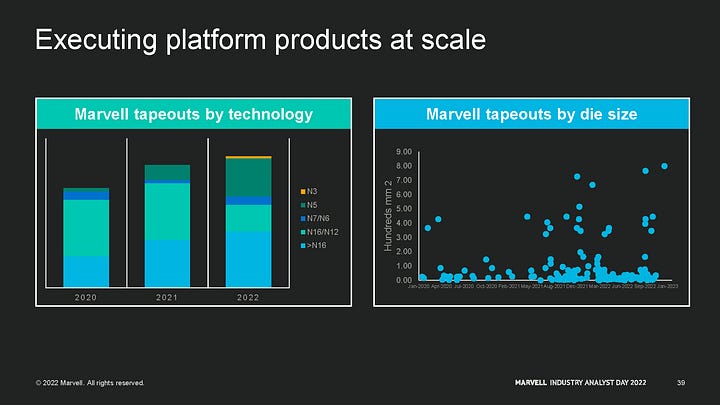

By combining some of the industry’s best SerDes, design techniques, verification, and advanced process technology, Marvell can target datacenter, carrier infrastructure, automotive, and enterprise networking. There was a big transition for Marvell with the 5nm process technology. Before with 7nm and 16nm, Marvell didn’t run their first test chips until more than a year after the process node went to high-volume manufacturing (HVM). Now with 5nm and 3nm, Marvell is running their first shuttles as soon as TSMC allows them to.

In April 2020, Marvell had a 112G SerDes on TSMC’s N5P process node. We presume this was Inphi, not Marvell itself. In 2022, Marvell ran two test chips, one on TSMC N3 and another on TSMC N3E. The prior helped them decide to skip N3, likely due to poor performance and power improvements, and the latter is what has allowed Marvell to test next-gen SerDes, DSP, and compute IP to accelerate time to market and competitiveness. The test chip contained IP from both Marvell and the Inphi acquisition.

It is noteworthy that Marvell has had 2 tapeouts >700mm^2 in just the last 6 months. More on that custom silicon effort later.

Marvell is heavily focused on system modeling, emulation, formal verification, and hybrid emulation of their silicon before they spend the massive amount required for a complete mask set. Marvell is setting itself up to avoid the dark side of the semiconductor renaissance that has plagued Intel and many other design organizations.

Marvell also strives to be the leader in the electro-optical domain. Inphi has that leadership for the ethernet world, and with the right investments and engineering, this could be extended beyond to all electrical and optical connections between packages and on-package.

For the long-reach optical market, Marvell dominates 112G PAM4 DSPs and TIAs and is trying to set itself up to do the same with the next-generation 224G. In the extremely long-reach coherent module market, Marvell is focused on maintaining leadership in 400G QAM 16 and next-generation 800G DSP, TIA, and pluggable transceivers. We are more skeptical of this working out in the co-packaged optics era with such stiff competition. Multiple companies such as Broadcom, Intel, Nvidia, and Ayar Labs are ahead of Marvell in productization timelines.

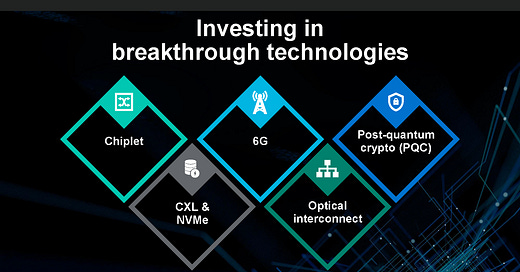

Advanced packaging is also critical to be a leader in the new era of semiconductors. Marvell currently does not utilize advanced packaging much in their products, but competitors such as AMD, Intel, Broadcom, and Nvidia do and have extensive experience. Marvell wants to catch up on this gap and exceed it, so they are focused on moving the entire lineup to more chiplet based. 3nm chiplets are generally planned have very little IO and focus moreso on the compute ASIC and low area die-to-die connections. 5nm chiplets will be used for SerDes and connectivity. Marvell is paying special care to the unique thermal challenges involved with advanced packaging.

DPU

One of the most important business units for Marvell is that of DPUs. It is the heart of infrastructure processing and is multi-faceted from 5G processing to networking cards and everything in between.

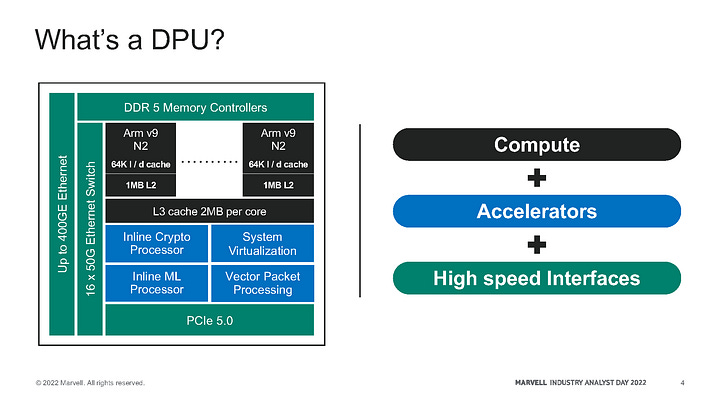

The DPU is a catch-all term for any product with compute, accelerators, and networking interfaces required for a specific task in a single package. Compare that to a standard CPU that doesn’t have accelerators or networking on the same chip—relying on external chips for accelerators and networking results in a solution that consumes too much power, limiting use in infrastructure platforms.

The history of the DPU is fascinating. Nvidia popularized the use of the word with the marketing of their Bluefield 2 DPU, but Marvell argues they have had DPUs for ~17 years via the Cavium legacy. The Cavium legacy is also where the security business and capabilities come from.

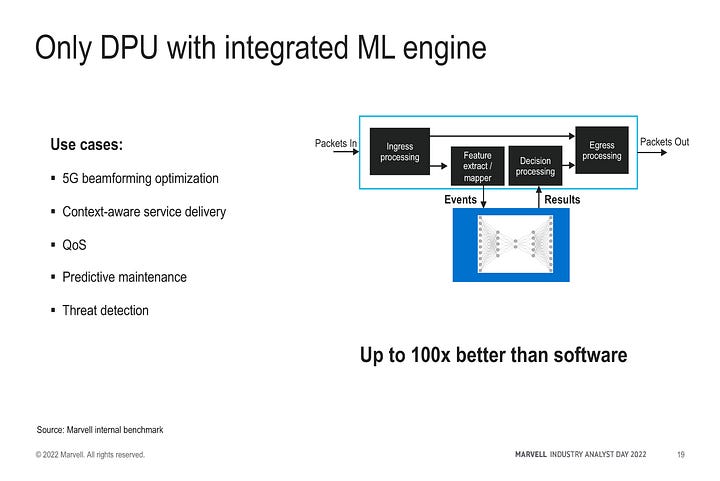

This generation of DPUs is quite versatile. Marvell’s use of Arm’s N2 core, in-house accelerators for 5G, machine learning, cryptography, virtualization, packet processing, and extensive ethernet capabilities gives them the right IP to deliver infrastructure-optimized DPUs to many markets.

In addition, they have stacked up multiple offerings in this space, having taped out 4 different dies for the market, while every other firm has taped out 1 die. This enables Marvell to cover a much more comprehensive array of use cases. The CN102 is 16 to 24 cores depending on the configuration, in addition to 6 channels of DDR5, 48MB of cache, and 200G Ethernet, all in a TDP of ~40W. This chip can also be co-packaged with a switch which gives it nearly 1Tb of ethernet switching capacity.

The lower-end CN103 and CN102 chips target significantly lower power and performance levels. Furthermore, there is a 4th product line for the 5G. There is a different DPU400 listed on that product sheet, but it is much further away from productization. The tapeout timeline for DPU400 is more like mid to late next year.

The target areas for these DPUs include cloud datacenters, the core network, edge datacenters, enterprise, and small businesses, and telecommunications networks. This includes virtual firewalls, load balancers, network security, vRAN at the edge, content distribution networks, channel management, routing, beamforming, and smartNIC use cases.

Marvell talked a lot about the open software stack they support, but many users have been disappointed by the software quality of the DPUs. It will be interesting to see how they will improve the software. The slides don’t mention IPDK, but Marvell is a founding member of the OPI and will be supporting IPDK longer term.

It should also be noted that for cloud hyperscale DPU use cases, it seems as though AMD’s Pensando, Intel’s Mount Evans, and Amazon’s Nitro have all found a major public cloud they can service (Microsoft, Google, AWS). It will be interesting to see if Marvell can get any wins here.

More about this topic will be covered in the custom silicon section. Marvell’s strategy with future generation DPU’s is a lot more compelling.

The performance metrics they showed were mostly in comparison to the competing DPUs from Intel and Nvidia in the CPU core department. Marvell also compared their crypto accelerator to that of Intel’s in their Icelake Xeon D lineup.

5G DPU

The 5G market is one that Marvell is gaining share rapidly. While the hype cycle for 5G has reached a trough, the network buildout are nowhere close to complete, even in developed markets. The number of 5G subscribers is ~10%, but by 2025, that number will reach 25% and the total traffic of that 25% is estimated to be 45% of traffic.

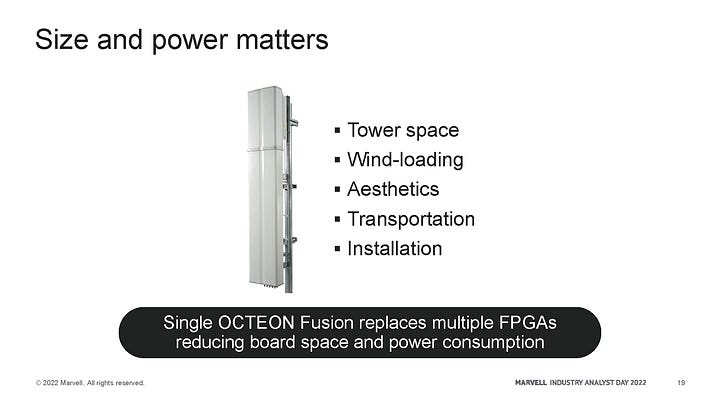

With 6 million macro radios deployed annually, the potential volume and sales for telecom-focused silicon could be huge. The compute demands for beamforming and L1, L2, and L3 processing are huge as channels go from 20MHz to 100MHz and MIMO goes from 4x4 to 32x32. While the 5G hype cycle went into overdrive, the upgrades that happen to networks over the next decade will unlock all the value that people shilled 5G as adding from day 1.

The radio access network dominates the power consumption of mobile telecom networks, so the accelerators for it are critical.

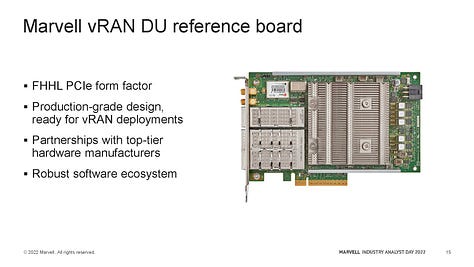

Marvell is one of the only companies besides Intel currently offering accelerated L1 processing and robust CPU cores for L2 and L3 with powerful networking. The difference is that Marvell’s acceleration is inline instead of lookaside.

Inline accelerators are integrated into the main processing path, allowing it to process data as it passes through the system. This can provide a significant speedup for certain types of operations, but it can also increase the system’s complexity and limit its flexibility. Ultimately, this is better for power consumption.

Contrast that with the current offering by Intel, which uses lookaside. The accelerator is not integrated into the main processing path. Instead, the main processor sends data to the accelerator for processing and retrieves the results, which are stored in a separate memory location. This provides less significant speedup and power benefits compared to inline acceleration, but it can also be more flexible and easier to implement. It should be noted that Intel will be adding inline acceleration while retaining flexibility with custom CPU instructions in Sapphire Rapids EE.

While the number of radio units being deployed is going to go down, the content per radio unit is going to soar. As the complexity increases, as will the amount of processing that occurs in the radio unit versus the distributed unit.

Marvell also happened to land Nokia as a client in their custom silicon division. If you paid attention half a decade ago, Intel killed Nokia’s Reefshark SoC through their incompetent “custom foundry” with 10nm. Nokia still hasn’t recovered since, but their partnership with Marvell may help. More about this in the custom silicon section.

PHY

PHY is a type of integrated circuit that is designed to handle the physical layer of networking responsible for converting digital data into a physical form that can be transmitted over a communication channel. In the case of Ethernet, for example, the PHY chip would convert digital data into electrical signals that can be sent over a copper wire.

PHYs can range from those on chips for driving direct attached passive copper to active cabling to retimers to PAM4 DSPs to coherent DSPs.

Marvell’s PHY business is central to all its business units, from custom ASICs, CXL chipsets, coherent modules, datacenter ethernet, automotive ethernet, SSD and HDD controllers, PAM4 modules, and DPUs.

One of the interesting areas Marvell is attacking is active electrical cables. While direct attached copper is the most common form of cabling and optical has traditionally been used for long-distance runs, active electrical cables are still relatively new for datacenter communications.

Active electrical cables contain electronic components that allow the cable to perform additional functions, such as amplifying or conditioning the electrical signal transmitted through the cable. In general, active electrical cables are more expensive than passive cables, which do not contain any built-in electronic components. However, they can offer improved performance and additional functionality while being cheaper than optical.

The fact Marvell is attacking this market with their Alaska AEC is very bad for Credo $CRDO.

Electro-optical Connectivity

The PHY business and electro-optical connectivity both come from the Inphi acquisition. Inphi’s claim to fame was with PAM4 signaling.

PAM4 is a signaling technique used in high-speed communication systems, such as Ethernet. PAM stands for pulse amplitude modulation, and the "4" in PAM4 refers to the number of levels used to encode the data. In PAM4 signaling, each bit of digital data is represented by one of four different amplitude levels, rather than the two levels used in traditional binary signaling (0 and 1), allowing more data to be transmitted over a given channel compared to conventional NRZ signaling.

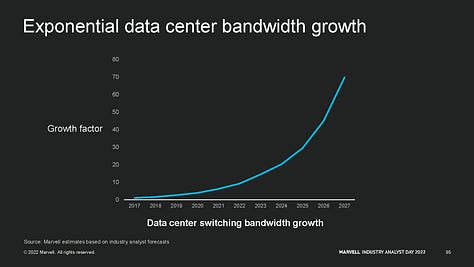

PAM4 gives 30% lower power and cost per bit of data transferred. Marvell is now shipping 800G, and the primary market for this is AI clusters. BW demands have generally doubled every 3 years, but AI is at the beginning of its S curve and is accelerating those demands. Broadcom is bringing very strong competition in this market, although they currently have a much lower share in 400G PAM4.

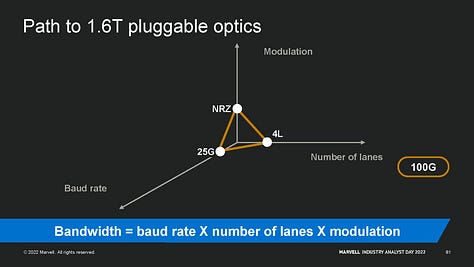

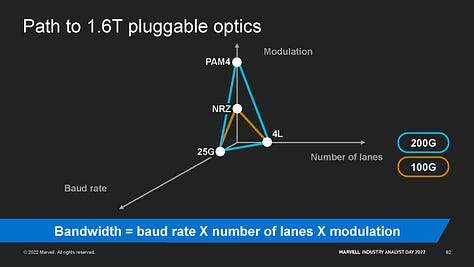

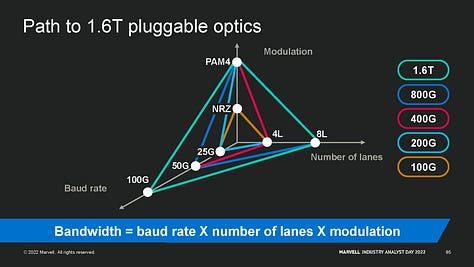

Marvell showed the progression of the in-datacenter pluggable market with a nice matrix. NRZ (2 bits per clock) at 25G data rate with 4 lanes was what the 100G generation was based on. 200G moved to PAM4, allowing each lane to be driven twice as fast. This is when the Inphi business took off. Microsoft was a big adaptor of 200G PAM4 from Inphi due to the superior cost and power. All the other hyperscalers followed soon after.

400G doubled the data rate. 800G doubled the number of lanes to 8. The 1.6T generation is under contention. Some companies want to move to 16 lanes, while Marvell is pushing for doubling the datarate of the PHYs to 224G PAM4 from 112G PAM4. Marvell is sampling this product today.

One interesting observation is that Marvell offers DSPs and TIAs externally for others to integrate into pluggable transceivers, but in the coherent optical market, they mostly sell their in-house pluggable transceivers.

Datacenter Switches

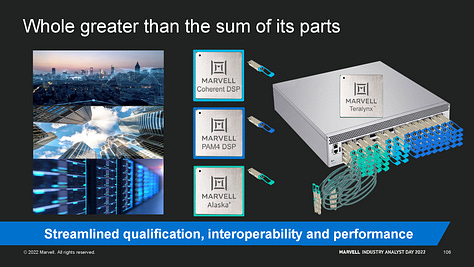

Marvell’s most recent acquisition was for Innovium and their Teralynx switch lineup. Marvell, despite having two other switch lineups, acquired a 3rd lineup. Marvell argues that the features required for datacenter switching differ significantly from those of the other markets. In the case of the datacenter market, the bandwidth demands are soaring at an exponential rate.

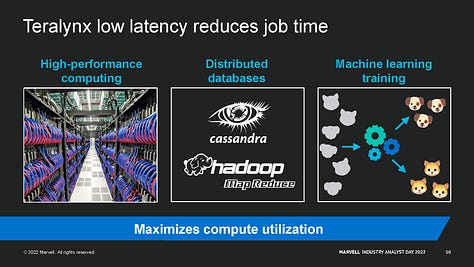

Hyperscale datacenter switches require much lower latency and advanced telemetry for congestion management. Teralynx boasts having some of the best latency, but we have heard and seen conflicting information which shows Broadcom and Nvidia InfiniBand and much lower latency.

The datacenter switching market is very competitive between Broadcom’s dominance, Nvidia’s rise with Spectrum-4 ethernet and InfiniBand, Cisco fighting aggressively to stop share losses, and Intel’s lofty aspirations with Tofino. We are skeptical of Marvell’s Teralynx ability to gain a serious amount of share.

This is compounded by the fact that the current generation switches from Marvell still only support 12.8T which Nvidia and Broadcom are now shipping 51.2T in small volumes. Marvell is going to try to leapfrog two generations in rapid succession, directly to 51.2T, but their entrance into the 25.6T and 51.2T generation is clearly very late, even later Intel and Cisco who are shipping 25.6T generation switches. Some of our sources say Marvell had silicon-level problems on 25.6T that required them to scrap that design.

We asked Nariman Yousefi of Marvell about entrance into the routing silicon business. Marvell has many pieces of IP from excellent PHYs to control plane and data plane processing, but his argument was that there wasn’t space for them as it is a lower volume market. Between captive of Juniper Networks and Cisco and very competitive silicon from Broadcom, it doesn’t make much sense for them to pursue this market.

The 2nd half of this write-up will be for subscribers only and it will cover automotive, storage, custom silicon with hyperscalers, including storage, security, a huge AI training chip, AI inference, custom DPUs, custom video ASICs, and 9 different CXL product lines.

We will also share our FY 2023, 2024, and 2025 revenue and EPS estimates in the subscriber only section.

Automotive

In the automotive semiconductor market, most focus on a few major drivers. One is power semiconductors where silicon carbide (SiC), gallium nitride (GaN), and even IGBTs dominate the conversation. The other is with ADAS and self-driving, where chips from Mobileye, Nvidia, and Intel dominate the conversation. One layer deeper and there is a lot of discussion about sensors from CMOS image sensors to Radar to Lidar. There is a critical component of this supply chain that many are missing when having this conversation about the megatrend of semiconductors in automotive, and Marvell may have the answer.

It is important to note that most automotive OEMs want to control their own destiny, not be locked into a single platform. Furthermore, they want to be able to differentiate based on software. While success is only guaranteed for some OEMs, it is just as important to consider where they will spend their efforts. As such, they must leverage common platforms, that can still be tweaked and customized to their liking.